Dla każdej pracy dyplomowej wyszczególniono: temat, [opiekuna] , szczegóły pracy oraz zamawiającego (firma, projekt badawczy itp.)

Kolory oznaczają:

- zielony — temat wolny

- czerwony — temat zajęty (realizacja w toku)

- czarny — temat już zrealizowany

2022

52. Akcelerator AI w układzie FPGA.

Opracowanie i uruchomienie w układzie FPGA akceleratora AI do detekcji na obrazie z wykorzystaniem frameworku Gstreamer. Akcelerator ma bazować na sieci przygotowanej w dowolnym środowisku. Przygotowane wagi sieci mają pozwolić na detekcję z użyciem funkcji aktywacji. Platforma sprzętowa: płyta TySOM-3-ZU7EV (Xilinx Zynq UltraScale+). Wymagana dobra znajomość HDL. Praca w kooperacji z firmą Aldec.

51. Transaktor interfejsu Open NAND Flash.

Opracowanie i uruchomienie transaktora do weryfikacji protokołu Open NAND Flash Interface według standardu Accellera SCEMI. Wymagana dobra znajomość HDL. Praca w kooperacji z firmą Aldec.

50. Transaktor protokołu sFPDP.

Opracowanie i uruchomienie transaktora do weryfikacji protokołu sFPDP (VITA 17.1–2015 sFPDP) według standardu Accellera SCEMI. Wymagana dobra znajomość HDL. Praca w kooperacji z firmą Aldec.

49. Transaktor magistrali EP100 PowerPC Bus.

Opracowanie i uruchomienie transaktora do weryfikacji magistrali EP100 PowerPC według standardu Accellera SCEMI. Wymagana dobra znajomość HDL. Praca w kooperacji z firmą Aldec.

48. Transaktor magistrali MIL-STD-1553B.

Opracowanie i uruchomienie transaktora do weryfikacji magistrali MIL-STD-1553B dla awioniki według standardu Accellera SCEMI. Wymagana dobra znajomość HDL. Praca w kooperacji z firmą Aldec.

47. Transaktor magistrali CAN.

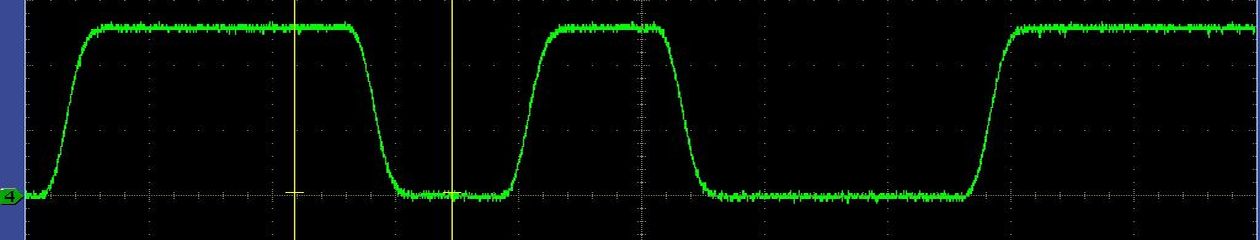

Opracowanie i uruchomienie transaktora do weryfikacji magistrali CAN (Controller Area Network) według standardu Accellera SCEMI. Wymagana dobra znajomość HDL. Praca w kooperacji z firmą Aldec.

2021

46. Implementacja sprzętowa oscylatora sterowanego cyfrowo, współpraca z Aldec

45. Sprzętowa implementacja filtru różniczkującego na potrzeby radia programowalnego, współpraca z Aldec

2020

44. Opracowanie i uruchomienie gry typu "Tetris" w układzie FPGA, współpraca z BTC Korporacja

43. Opracowanie i uruchomienie gry typu "Pong " w układzie FPGA, współpraca z BTC Korporacja

42. Podsystem obsługi wirtualnego interfejsu JTAG w układzie FPGA, współpraca z BTC Korporacja

41. Podsystem obsługi wyświetlacza dotykowego LCD w układzie FPGA, współpraca z BTC Korporacja

40. Podsystem tekstowego monitora HDMI w układzie FPGA, współpraca z BTC Korporacja

2019

39. Sprzętowa implementacja modułu kompresji danych, współpraca z SemiHalf

38. Opracowanie i uruchomienie gry typu "Snake " w układzie FPGA, współpraca z BTC Korporacja

37. Podsystem obsługi kodeka audio na platformie Zynq (FPGA + ARM, ZYBO), projekt własny

36. Podsystem obsługi frame grabbera HDMI na platformie Zynq (FPGA + ARM, ZYBO), projekt własny

35. Podsystem obsługi GPIO i PS/2 na platformie Zynq (FPGA + ARM, ZYBO), projekt własny

2018

34. Sterownik napędu CD przez interfejs SATA, JK, współpraca z Ancient Audio

33. Opracowanie i uruchomienie gry typu "Space shooter" w układzie FPGA, JK, współpraca z BTC Korporacja

32. Syntezer dźwięku w układzie FPGA, JK, współpraca z BTC Korporacja

31. Moduł interfejsu odczytu mierników z interfejsem wizyjnym i dostępem zdalnym, JK, projekt własny

30. Syntezowalny model kontrolera I2S, PJR, współpraca z DCD

29. Rejestrator danych cyfrowych na karcie microSD, PJR, współpraca z BTC Korporacja

2017

28. Interfejs Ethernet dla węzła magistrali KNX/EIB, JK, własny

27. Gra Arkanoid, PJR, projekt własny

26. Sterownik kostki LED, PJR, współpraca z BTC Korporacja

25. Generator sygnałowy DDS, PJR, współpraca z BTC Korporacja

24. Dydaktyczny model sterownika interfejsu HDMI w układzie FPGA, PJR, współpraca z BTC Korporacja

23. Dydaktyczny model aplikacji Arkanoid w układzie FPGA, PJR, współpraca z BTC Korporacja

2016

22. Kontroler magistrali MVB, JK,współpraca z Radionika

21. Środowisko weryfikacji kontrolera magistrali MVB, JK, współpraca z Radionika

20. Interfejs kamery dla sterownika manipulatora kartezjańskiego, JK, projekt własny

19. Bramka IP dla systemu KNX/EIB, JK, projekt własny

2015

18. Tester stabilności referencyjnego źródła częstotliwości kontrolera BTS, JK, współpraca z Nokia

17. Model symulacyjny transceivera MGT, PJR, współpraca z Nokia

16. Moduł nawigacyjny dla awioniki, PJR, współpraca z Avionix

2014

15. Tester interfejsów radiowych CPRI – część sprzętowa, PJR, współpraca z Nokia

14. Tester interfejsów radiowych CPRI – część programowa, PJR, współpraca z Nokia

13. Interfejs pamięci DDR w układzie FPGA, PJR, projekt własny

2013

12. Projekt i wykonanie monitora pakietów Ethernet z wykorzystaniem karty NetFPGA10G, JK, projekt własny

11. Implementacja sprzętowa obliczeń kinematyki robota hybrydowego w układzie FPGA, JK, projekt własny

2012

10. Sprzętowa implementacja wybranych modułów algorytmu MACSec na karcie NetFPGA, JK, współpraca z KT AGH

9. Weryfikacja wybranych modułów sprzętowej implementacji algorytmu MACSec, JK, współpraca z KT AGH

8. Ewaluacja stanowiska uruchomieniowego Altium NanoBoard 3000, PJR, projekt własny

2011

7. Sprzętowa implementacja miksera audio w układzie FPGA, JK, projekt własny

6. Akceleracja symulacji wybranego sprzętowego kontekstowego filtru obrazu na platformie HES, JK, projekt własny

5. Akceleracja symulacji wybranego sprzętowego filtru FIR na platformie HES, JK, projekt własny

4. Modelowa symulacja projektu w układzie FPGA z interfejsem VHPI, JK, projekt własny

3. Modelowa symulacja projektu przetwarzania obrazu w układzie FPGA z interfejsem Simulink, JK, projekt własny

2. Modelowa symulacja projektu filtracji dźwięku w układzie FPGA z interfejsem MATLAB, JK, projekt własny

1. Model behawioralny przetwornika analogowo – cyfrowego AD9239, PJR, projekt własny